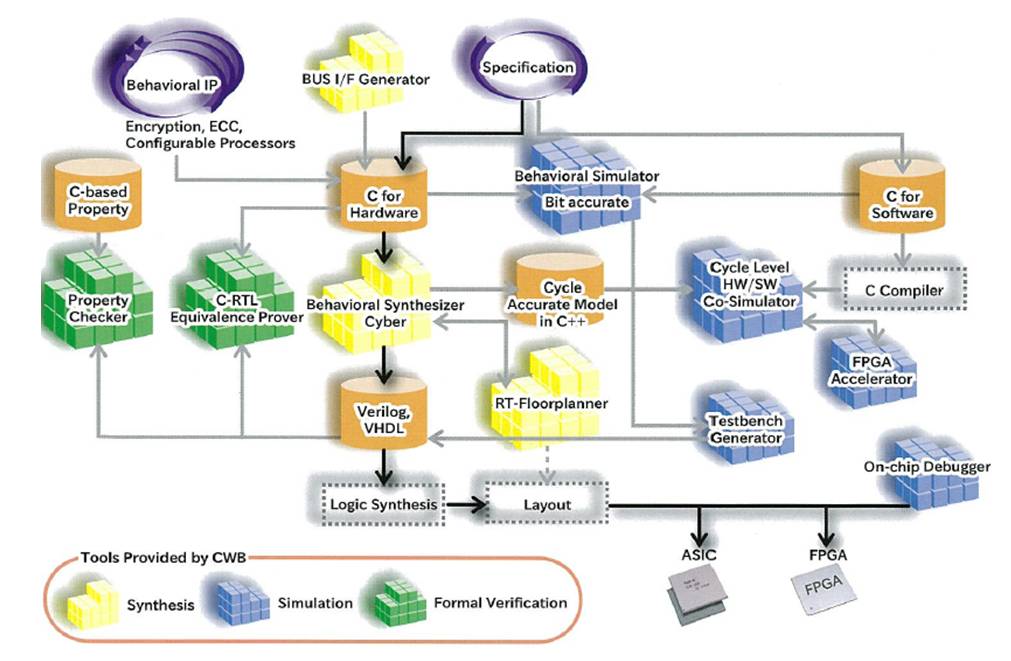

CyberWorkBench是一個以C語言進行LSI設計(系統層級的合成與驗證)的整合開發環境,所有工具均整合於CyberWorkBench,設計人員可以完全使用C語言 (ANSI-C / System C) 來設計和驗證晶片的動作,無須進行RTL(暫存器傳送層級)的除錯作業。

CyberWorkBench大幅縮短設計週期,在製造晶片前可驗證嵌入式SW,並且以高品質的合成結果(高效,小晶片尺寸及低耗電量)提供極為可靠的SoC(系統單晶片)設計。

先進的行為合成器(Behavioral Synthesizer):

- 高效率的合成處理,高品質的合成結果

- QoR (Quality of Results)的精確估算與分析

- 輕鬆進行反覆合成,找出最佳結果(面積vs性能間的取捨)

- 能作SoC設計中的多種調節(多時脈,同步/非同步重設,多種類記憶體,選通時脈,…)

- 支援ANSI-C(擴充語法)/ System C(多元陣列,結構體,指標,函數,轉移,迴圈,…)

不只是合成器,而是整合開發環境(IDE)的CyberWorkBench包括:

- 行為合成器(Behavioral Synthesizer)

- 匯流排界面產生器(Bus I/F Generator)

- 可自動產生AMBA-AHB/AXI介面以連接您的IP設計

- 硬體-軟體協調模擬器(HW-SW Co-Simulator)

- 高速(比RTL模擬器快10~100倍)的精確週期模型產生器 (Cycle-accurate Model Generator)

- 原始碼層級除錯器 (Source code Debugger)

- 使用FPGA的加速模擬器 (FPGA Accelerator)

- C語言和RTL的等效性驗證器(C-RTL Equivalence Prover)

- 屬性檢測器(Property Checker)

- 模擬測試平台產生器(Testbench Generator)

- 自動產生精確週期的RTL模擬測試平台(Testbench)

- 合成,分析及驗證用的GUI整合開發環境

|