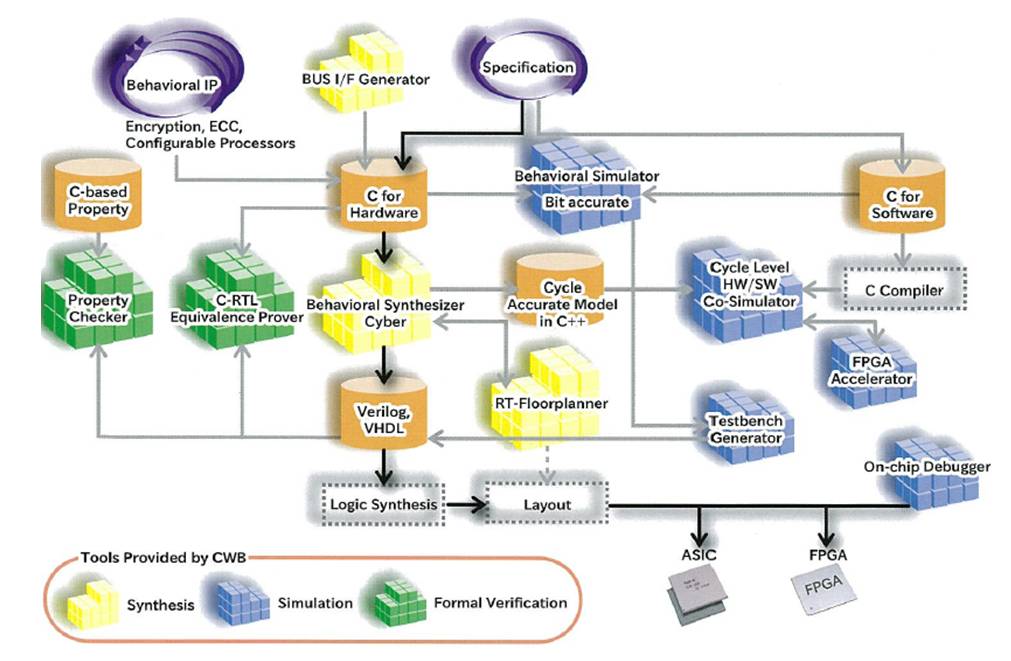

CyberWorkBench是一个以C语言进行LSI设计(系统层级的合成与验证)的整合开发环境,所有工具均整合于CyberWorkBench,设计人员可以完全使用C语言 (ANSI-C / System C) 来设计和验证芯片的动作,无须进行RTL(缓存器传送层级)的除错作业。

CyberWorkBench大幅缩短设计周期,在制造芯片前可验证嵌入式SW,并且以高质量的合成结果(高效,小芯片尺寸及低耗电量)提供极为可靠的SoC(系统单芯片)设计。

先进的行为合成器(Behavioral Synthesizer):

- 高效率的合成处理,高质量的合成结果

- QoR (Quality of Results)的精确估算与分析

- 轻松进行反复合成,找出最佳结果(面积vs性能间的取舍)

- 能作SoC设计中的多种调节(多频率,同步/异步重设,多种类内存,选通频率,…)

- 支持ANSI-C(扩充语法)/ System C(多元数组,结构体,指针,函数,转移,循环,…)

不只是合成器,而是整合开发环境(IDE)的CyberWorkBench包括:

- 行为合成器(Behavioral Synthesizer)

- 总线接口产生器(Bus I/F Generator)

- 可自动产生AMBA-AHB/AXI接口以连接您的IP设计

- 硬件-软件协调仿真器(HW-SW Co-Simulator)

- 高速(比RTL仿真器快10~100倍)的精确周期模型产生器 (Cycle-accurate Model Generator)

- 原始码层级除错器 (Source code Debugger)

- 使用FPGA的加速仿真器 (FPGA Accelerator)

- C语言和RTL的等效性验证器(C-RTL Equivalence Prover)

- 属性检测器(Property Checker)

- 模拟测试平台产生器(Testbench Generator)

- 自动产生精确周期的RTL仿真测试平台(Testbench)

- 合成,分析及验证用的GUI整合开发环境

|