## **Overview**

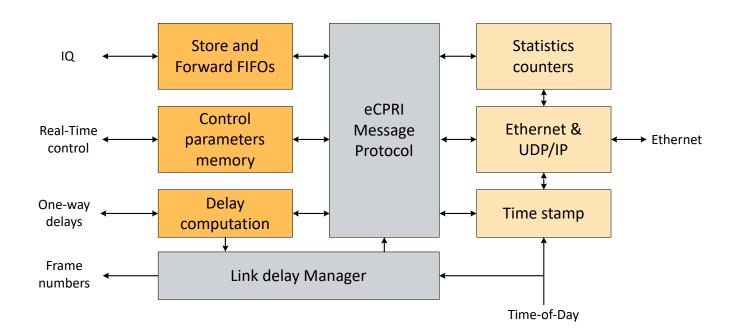

Chip Interfaces eCPRI core is a highly scalable and silicon agnostic implementation of the eCPRI standard targeting any ASIC, FPGA or ASSP technologies. The eCPRI implementation builds on long-time experience designing CPRI and Radio-Over-Ethernet solutions for fronthaul and delivers a flexible engine that is prepared for tight integration with software applications. The IP is designed to meet or exceed the requirements of radio systems, base band systems, fronthaul switches or advanced test systems. The speed optimized core can handle any solutions reaching from the "small footprint" to the most complex applications running 25 Gbps. The IP can dynamically be configured to handle wireless multimode radio systems enabling high-performance throughputs required by 4G and 5G wireless solutions.

## **Key Features**

| Richly Featured     | Support for frequency-domain IQ transport Support for various functional split between RU and BBU Supports 10G/25G Ethernet MAC ports Agnostically supports multiple synchronization schemes Wide flexibility for configuring |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Easy to use         | Testbench with typical system configuration and examples                                                                                                                                                                      |

| Silicon Agnostic    | Designed in HDL and targeting any RTL implementation like ASICs, ASSPs and FPGAs                                                                                                                                              |

| Highly Configurable | Supporting small to large system configurations                                                                                                                                                                               |

## **Specification**

| Feature Feature                                                                     | Availability                    | Default  | Option   | Comment |

|-------------------------------------------------------------------------------------|---------------------------------|----------|----------|---------|

| General Features                                                                    | Availability                    | Doradic  | Орион    | Commone |

| Standard                                                                            | eCPRI Specification V1.2        | <b>√</b> |          |         |

| Functional Splits supported                                                         | eCPRI splits A to E / intra-PHY | √        |          |         |

| Message Types Supported                                                             | 0: IQ data                      | <b>√</b> |          |         |

|                                                                                     | 1: Bit sequence                 | <b>√</b> |          |         |

|                                                                                     | 2: Real-time control<br>data    | <b>√</b> |          |         |

|                                                                                     | 3: Generic data transfer        | <b>√</b> |          |         |

|                                                                                     | 4: Remote memory access         | <b>√</b> |          |         |

|                                                                                     | 5: One-Way delay<br>measurement | <b>√</b> |          |         |

|                                                                                     | 6: Remote reset                 | <b>√</b> |          |         |

|                                                                                     | 7: Event indication             | <b>√</b> |          |         |

| Ethernet RX/TX traffic supported                                                    | 10G and 25G                     | <b>√</b> |          |         |

| Support mandatory eCPRI<br>EtherType                                                | Yes                             | <b>√</b> |          |         |

| Support filtering of inbound<br>Ethernet traffic based on MAC<br>and packet headers | Yes                             |          | <b>√</b> |         |

| Supported protocol stacks                                                           | IPv4/IPv6 and UDP               | <b>√</b> |          |         |

| VLAN tag insertion/removal                                                          | Yes                             | <b>√</b> |          |         |

| One-way delay measurement                                                           | 1-step and 2-step               |          | √        |         |

| Support jumbo frames with up to 9000 bytes of MTU payload                           | Yes                             | <b>√</b> |          |         |

| Configurable size of receive buffering for UL/DL                                    |                                 |          | <b>√</b> |         |

| Data (IQ) Interface                                                                 | Avalon streaming                | <b>√</b> |          |         |

|                                                                                     | AXI-S                           |          | √        |         |

| Delay Measurement                                                                   |                                 |          |          |         |

| Support for external timing source                                                  | Yes                             | <b>√</b> |          |         |

| ToD input bus width                                                                 | 80 bits                         | √        |          |         |

| Ethernet Interface                                                                  |                                 |          |          |         |

| Number of Ethernet ports<br>towards network transport<br>layer                      | 1                               | √        |          |         |

| Ethernet MAC interface standard                                                     | Avalon streaming                | <b>√</b> | ,        |         |

| Staridara                                                                           | AXI-S                           |          | √        |         |

| Feature                                                          | Availability      | Default  | Option   | Comment                                                    |

|------------------------------------------------------------------|-------------------|----------|----------|------------------------------------------------------------|

| CPU Interface                                                    |                   |          |          |                                                            |

| Internal register width                                          | 32 bits           | <b>√</b> |          |                                                            |

| IRQ support                                                      | Yes               | <b>√</b> |          |                                                            |

| Interface standards supported                                    | Avalon            | √        |          |                                                            |

|                                                                  | AXI4-Lite         |          | <b>√</b> |                                                            |

|                                                                  | APB               |          | <b>√</b> |                                                            |

| Clock and Reset                                                  |                   |          |          |                                                            |

| IP main clock frequency                                          | Up to 390.625 MHz | √        |          |                                                            |

| IP CPU register clock frequency                                  | 100 MHz           | √        |          |                                                            |

| IP Ethernet interface clock<br>frequency towards Ethernet<br>MAC | 156.25/390.625    | √<br>    |          | 10G/25G Ethernet support                                   |

| Separate resets for RX, TX and Register interface                | Yes               | <b>√</b> |          |                                                            |

| Deliverables                                                     |                   |          |          |                                                            |

| Code                                                             | SystemVerilog     | <b>√</b> |          | Source code or Encrypted RTL                               |

| Documentation                                                    | Yes               | <b>√</b> |          | Including User Manual and<br>Release Note                  |

| Simulation Environment                                           | Yes               | √        |          | Simple Test Environment,<br>Test Cases and Test<br>Scripts |

| Programming register specification                               | Yes               | <b>√</b> |          |                                                            |

| Timing Constraints in Synopsys<br>SDC format                     | Yes               |          | <b>√</b> |                                                            |

| Access to Support System                                         | Yes               | √        |          |                                                            |

| Synopsys SGDC Files                                              | Yes               |          | √        |                                                            |

| Synopsys Lint, CDC and<br>Waivers                                | Yes               |          | √        |                                                            |

**eCPRI IP Core**

Datasheet V. 1.0 - Aug 2023

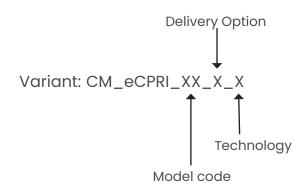

## **Ordering Info**

| Delivery Option code | Delivery Option Code   |

|----------------------|------------------------|

| В                    | RTL Source Code        |

| С                    | Encrypted FPGA Netlist |

| Technology code | Target Technology |

|-----------------|-------------------|

| A               | ASIC              |

| F               | FPGA              |

| Model code | Model description |

|------------|-------------------|

| 3          | eCPRI             |